# Nanotubes

Bauelemente für eine neue Nanoelektronik

Moritz Bubek

## Übersicht

- Struktur von Nanotubes

- Defekte an Nanotubes

- "klassischer" Schottky-Effekt

- Elektrische Eigenschaften von SWNTs SWNT-Schottky-Diode

- "klassischer" Feldeffekttransistor

- SWNT-FET

- Logische Schaltkreise

- Ausblick

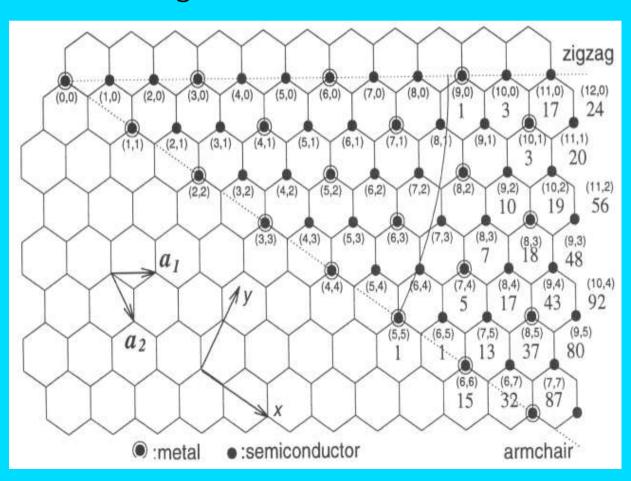

### Struktur von Nanotubes

Chiral-Vektor:  $C_h = n a_1 + m a_2$

Durchmesser abhängig von n und m:  $d_t = C_h/\pi$

durch Berechnung der Bandenergien findet man:

alle (n,n) sowie alle 2n+m=3q haben metallische Struktur

der Rest ist halbleitend

### Struktur von Nanotubes

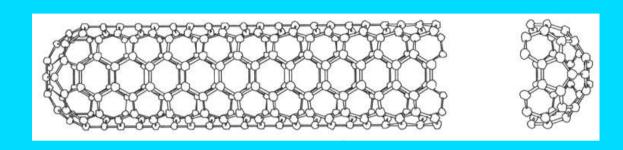

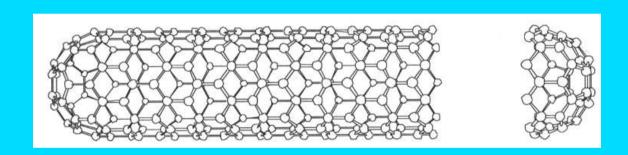

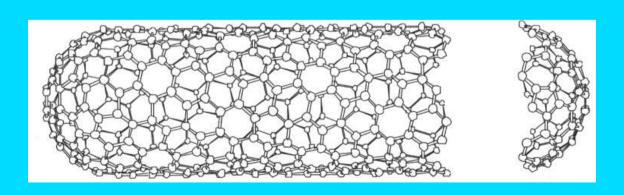

armchair (5,5)  $d_t$ =6.88 A  $\theta$ =30°

zigzag (9,0)  $d_t=7.15 A$  $\theta=0^\circ$

chiral tube (10,5)  $d_t = 10.5 \text{ A}$  $0 < \theta < 30^{\circ}$

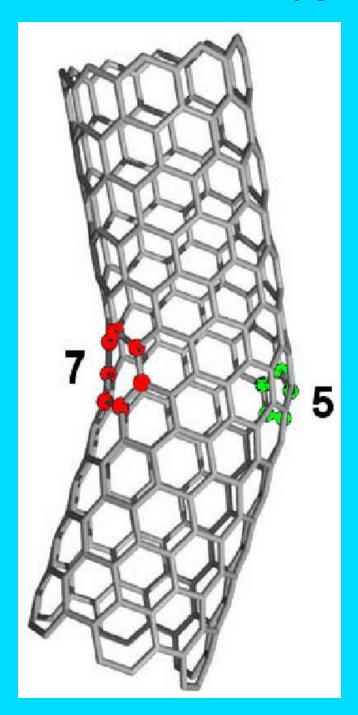

### Nanotube Defekte

topologische Defekte (5 bzw 7-Eck) erzeugen einen Knick (40°)

Übergang von "armchair" zu "zigzag"

AFM: SWNT auf Goldkontakten

andere Deformationen -> Knick aber entspricht nicht Experiment

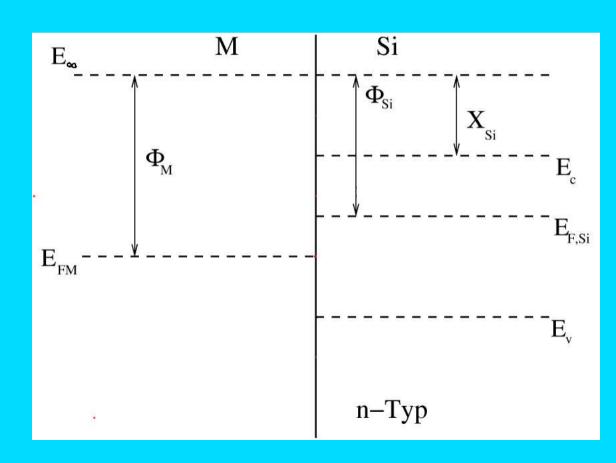

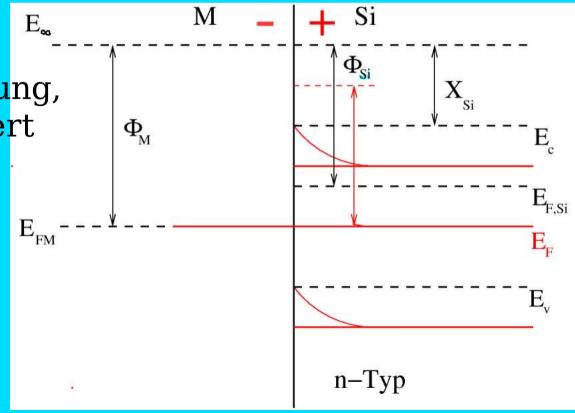

# Schottky-Effekt

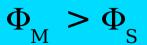

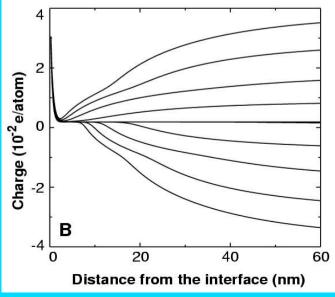

Metall-Halbleiter-Kontakt

$\Phi_{_{\mathrm{M}}}$ ,  $\Phi_{_{\mathrm{Si}}}$ : Austrittsarbeit,  $X_{_{\mathrm{Si}}}$ : Elektronenaffinität des Si

Energiezustände der getrennten Systeme

# Schottky-Effekt

Bei Kontakt muß am Übergang  $E_{F,M} = E_{F,Si} = E_F$  gelten

Si-Zustände "rutschen" runter, beide Fermi-Energien gleich

weil das Leitungsband des Si höher als das des Metalls liegt, würden Elektronen von Si zum Metall abfließen

Aufbau einer Gegenspannung, die das Abfließen verhindert

Bandverbiegungsbereich: Verarmung an Elektronen, RLZ

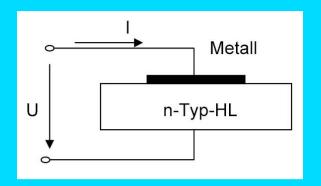

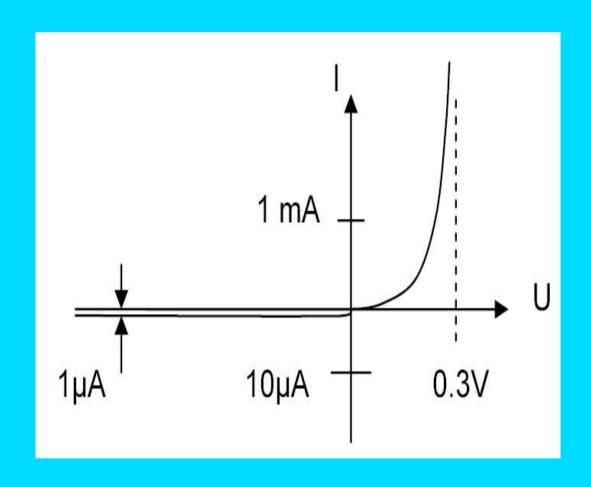

# Schottky-Diode

Bauelement aus Metall-HL-Übergang, durch Aufdampfen von Metall hergestellt

hohe Schaltgeschwindigkeiten (vgl HL-HL) da Strom nicht von Diffusion abhängt

Einsatz als Microwellengleichrichter, bis ca. 10 GHz

relativ kleine Schwellspannung, festgelegt durch  $\Phi_{\rm M}$ - $\Phi_{\rm HL}$

sehr rauscharm

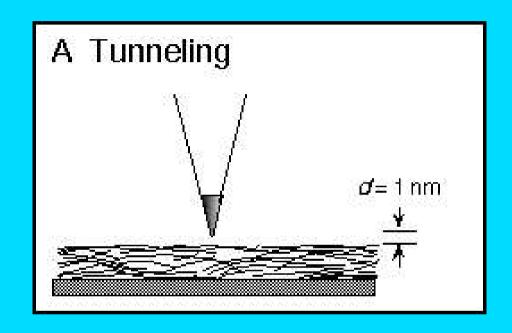

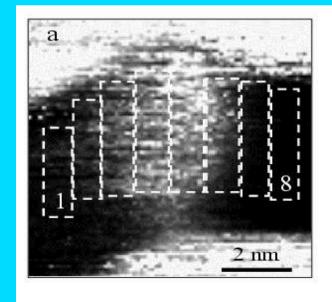

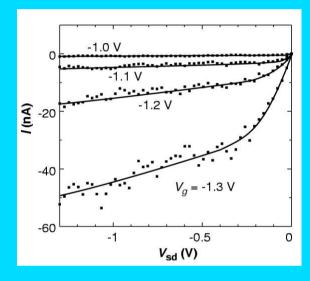

Experiment: Collins, Zettl, Smalley

Bestimmung der elektrischen Leitfähigkeit entlang eines SWNT mit Hilfe eines STM

dazu werden Strom-Spannungs-Kennlinien an mehreren Stellen aufgenommen

mit LASER-Ablation werden "armchair"-SWNTs erzeugt

Eigenschaften: metallisch, Durchmesser 1.36 nm

Bildung von "Bündeln" aus mehreren NTs

Aufpressen der erzeugten NTs auf ein goldbeschichtetes Glas

Pt-Spitze des STM wird über den Film aus SWNTs geführt, man erhält die lokale Zustandsdichte der Elektronen

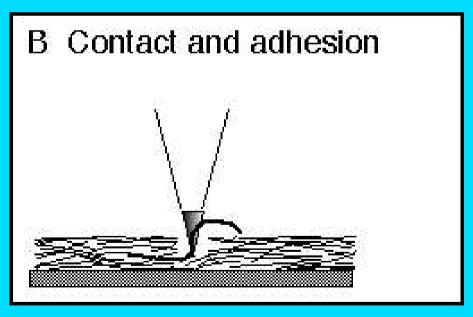

Spitze wird vorwärts gefahren, sie "tauch" in den Film ein (ca. 100 nm)

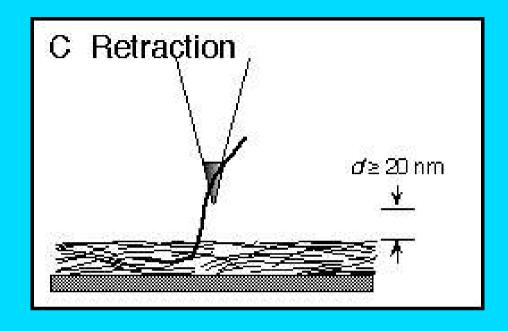

Spitze wird weiter rausgezogen (vgl Tunnelabstand in A)

durch Adhesion bleiben der NT mit der STM-Spitze verbunden

elektrischer Kontakt bleibt erhalten

Bindung an Spitze durch van-der-Waals-Kräfte Bündel von SWNTs ebenfalls durch vdW gebunden MWNTs nicht, keine Adhesion an der Spitze

nur an NTs, die bei 200-300 nm Entfernung noch Kontakt haben wird Leitfähigkeit gemessen (ca. 5%)

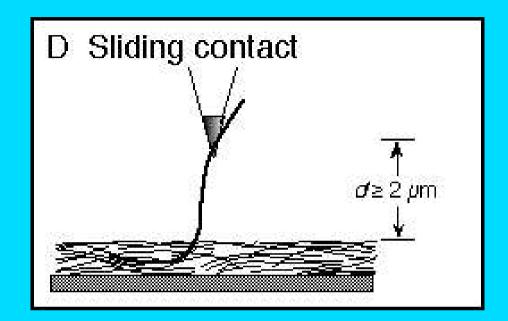

Spitze rutscht entlang des NT, 2 nm Schritte (bis Abriss)

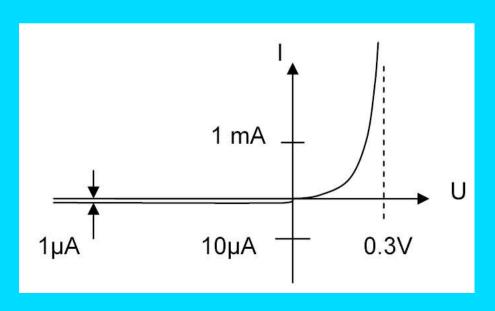

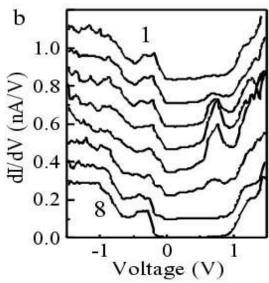

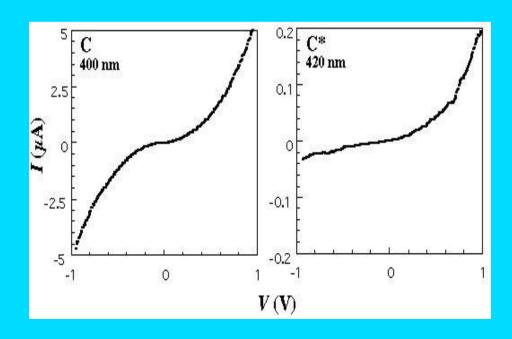

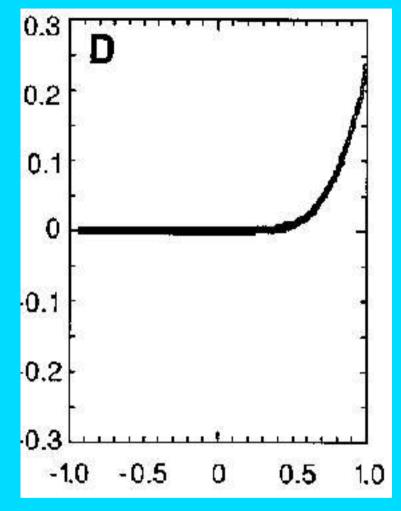

jeweils ein I-U-Diagramm Bereich -1 bis 1V)

nach Abreissen Messung nicht wiederholbar

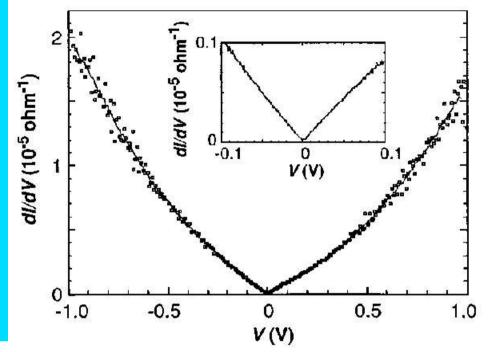

typische differentielle Leitfähigkeit eines SWNTs

(aus anderen Experimenten)

karakterisiert Zustandsdichte

Änderung sich beim Übergang zw. verschiedenen NTs

A: 1600 nm

B: 1850 nm

C: 1950 nm

D: 1980 nm

# A, B und C nicht linear, aber symetrisch

#### D zeigt ein gleichrichtendes Verhalten

vgl. mit Schottky-Kennlinie

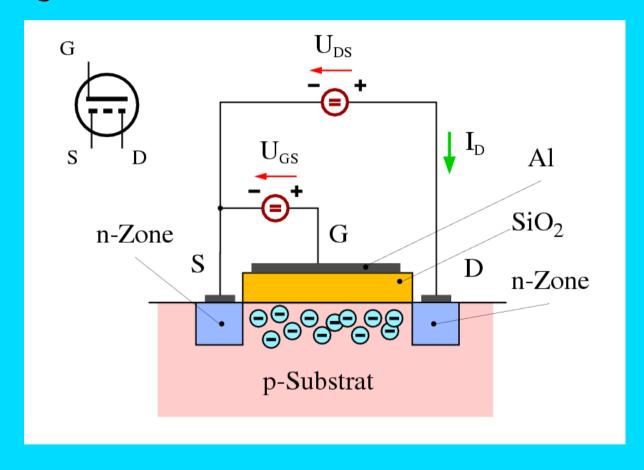

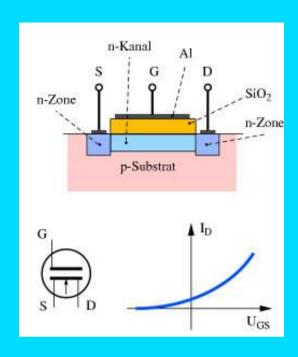

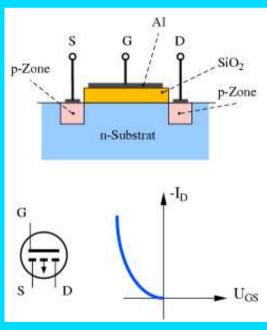

### Feld Effekt Transistoren

ein FET hat 3 Anschlüsse, Source, Drain und Gate S und D sind durch einen Halbleiterkanal verbunden

beim MOS-FET ist das Gate vom Kanal durch eine 100nm dicke Siliziumoxid-Schicht getrennt

die Leitfähigkeit des Halbleiter-Kanals wird mittels eines elektrischen Felds am Gate gesteuert

im Gegensatz zu Bipolaren Transistoren wird der FET leistungslos gesteuert

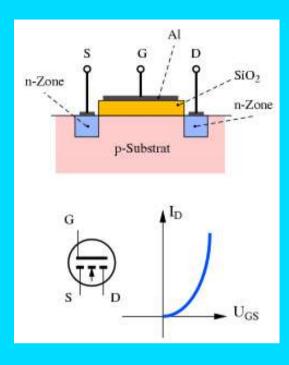

### Feld Effekt Transistoren

durch Influenz werden gegenüber dem Gate negative Ladungen angesammelt: n-Kanal

es gibt p-Kanal als auch n-Kanal MOS-FETs

zusätzlich zum abgebildeten Anreicherungstyp gibt es auch den selbstleitenden Verarmungstyp

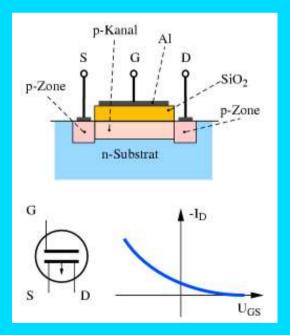

### Feld Effekt Transistoren

n-Kanal

p-Kanal

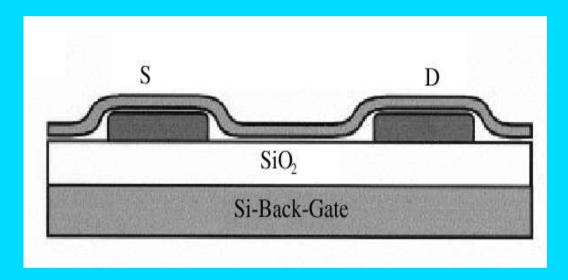

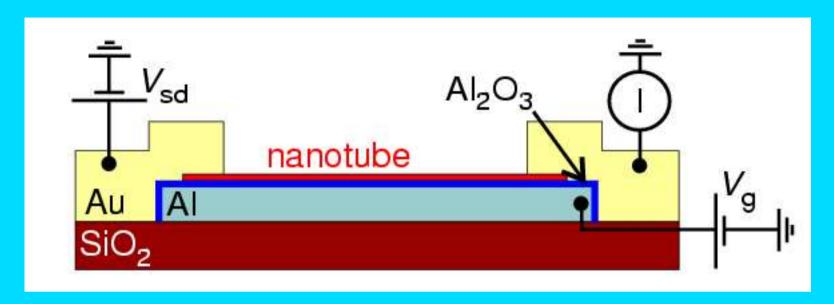

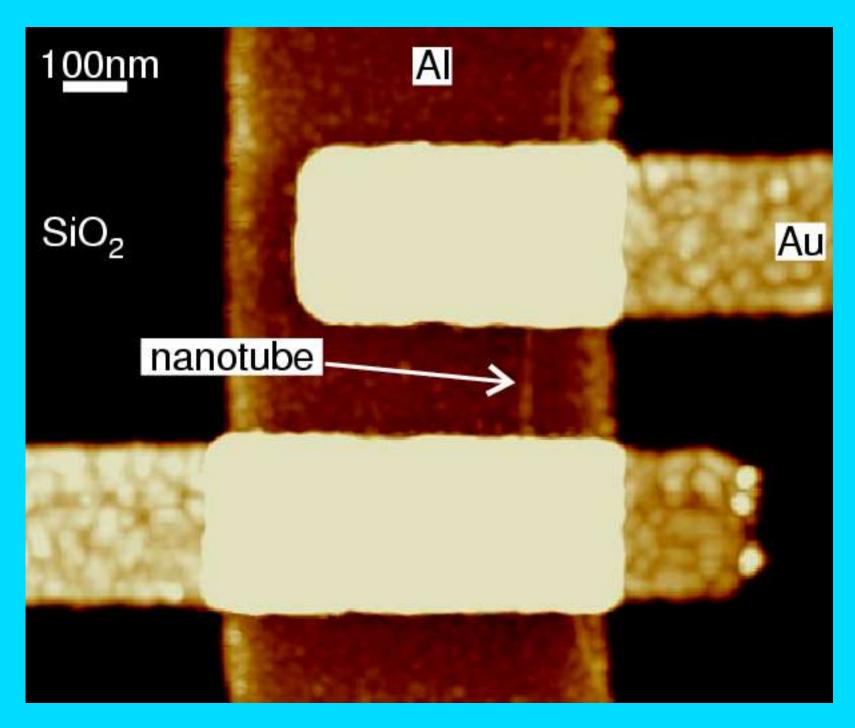

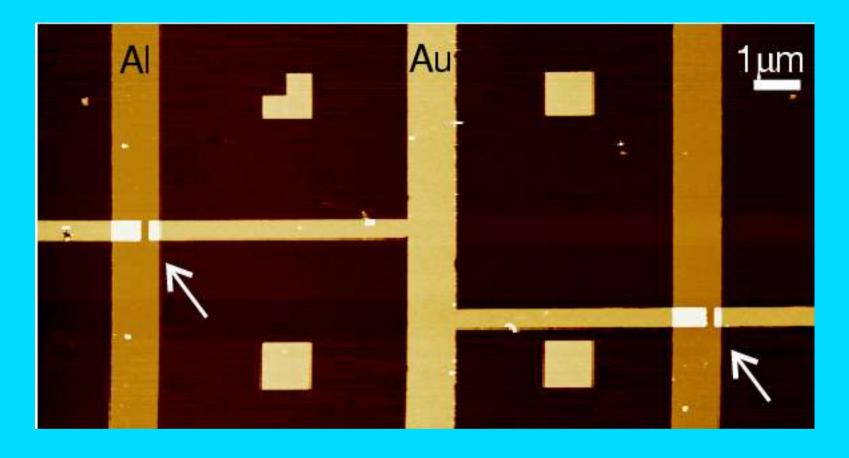

**Experiment: Bachtold**

für einen NT-FET braucht man Source und Drain Kontakte der Kanal wird durch ein Nanotube dargestellt

für das Gate gibt es mehrere Varianten:

Back-Gate, aufgebaut wie der "klassische FET"

Variante mit dem Gate als Leiterbahn ohne extra Isolatorschicht (nur oxidierte Isolatorbahn) diese ermöglicht integrierte Schaltungen

auf einen oxidierten Si-Wafer wird per Elektronenstrahl-Lithographie eine Aluminiumbahn aufgebracht (sie oxidiert )

SWNTs werden mittels Laser-Ablation erzeugt

Verteilung auf dem Wafer mit einer Dichlorethanlösung

mit AFM werden NTs (1 nm) auf die Al-Kontakte gebracht

S und D Kontakte und Bahnen aus Au per ESL aufgedampfen

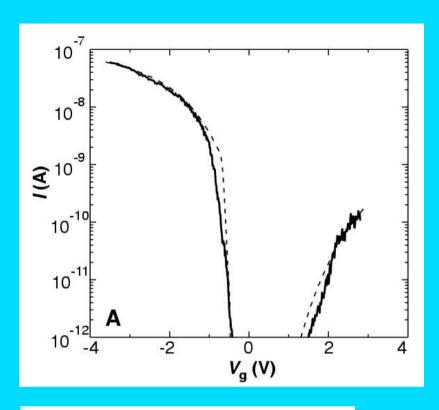

die I-U<sub>g</sub>-Kennlinie entspricht der eines p-Kanal-FETs

je nach Potential des Gates ist der NT unterschiedlich dotiert

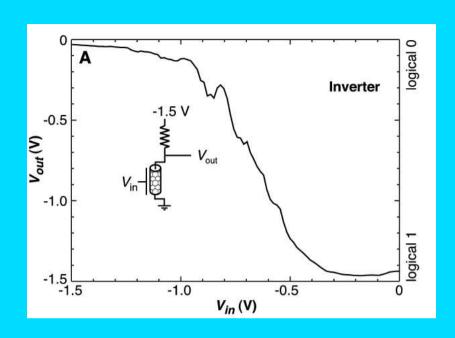

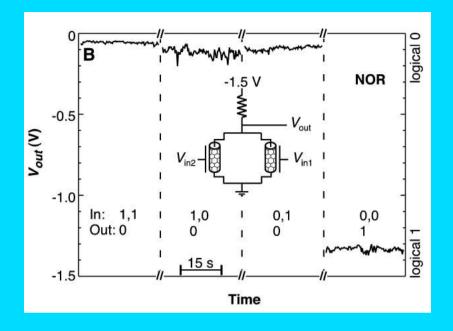

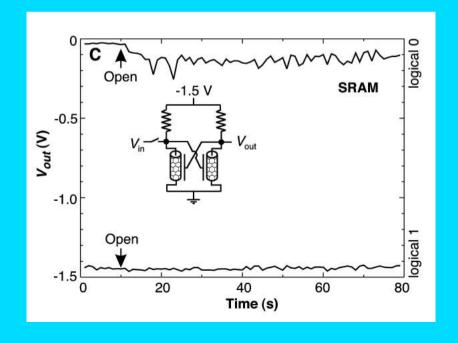

## Logische Schaltkreise aus SWNT

man benötigt mehrere Transistoren auf einem Wafer

außerdem muß der "Gain" des FETs mindestens 1 sein

### Logische Schaltkreise aus SWNT

### Ausblick

großer Schritt Richtung Nanoelektronik: Schaltkreise aus NT

Bauteile in Molekülgröße möglich

Beschränkung nur durch Zuleitung, der eigentliche FET ist ca 0.0025 µm² groß (heutige Prozessoren brauchen ca 2 µm²/FET (AMD, Hammer))

#### Probleme:

noch keine Möglichkeit viele NT zu positionieren

keine "selektive" NT-Produktion

Kontrolle der Chiralität beim Wachstum

#### Quellen:

```

"Nanotube Nanodevices", Collins et al., Science Vol 278, p 100

"Logic circuits with Carbon Nanotube Transistors", Bachtold et al., Science Vol 294, p 1317

"Single- and multi-wall carbon nanotube FETs", IBM, Apllied Physics Letters, Vol 73.17, p 2447

"Science of Fullerenes and Carbon Nanotubes", Dresselhaus, academic press und weitere:-)

```